#### About this Manual

We've added this manual to the Agilent website in an effort to help you support your product. This manual is the best copy we could find; it may be incomplete or contain dated information. If we find a more recent copy in the future, we will add it to the Agilent website.

#### **Support for Your Product**

Agilent no longer sells or supports this product. Our service centers may be able to perform calibration if no repair parts are needed, but no other support from Agilent is available. You will find any other available product information on the Agilent Test & Measurement website, <u>www.tm.agilent.com</u>.

#### HP References in this Manual

This manual may contain references to HP or Hewlett-Packard. Please note that Hewlett-Packard's former test and measurement, semiconductor products and chemical analysis businesses are now part of Agilent Technologies. We have made no changes to this manual copy. In other documentation, to reduce potential confusion, the only change to product numbers and names has been in the company name prefix: where a product number/name was HP XXXX the current name/number is now Agilent XXXX. For example, model number HP8648A is now model number Agilent 8648A.

# Installation/Service/Terminal Interface User's Guide

Motorola 6830x-Family Emulator/Analyzer HP 64798C/E/F

## Notice

Hewlett-Packard makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

© Copyright 1996, 1997, Hewlett-Packard Company.

This document contains proprietary information, which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Hewlett-Packard Company. The information contained in this document is subject to change without notice.

MS-DOS(R) is a U.S. registered trademark of Microsoft Corporation.

UNIX(R) is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company Limited.

Windows(R) and MS Windows(R) are U.S. registered trademarks of Microsoft Corp.

Hewlett-Packard Company P.O. Box 2197 1900 Garden of the Gods Road Colorado Springs, CO 80901-2197, U.S.A.

**RESTRICTED RIGHTS LEGEND.** Use, duplication, or disclosure by the U.S. Government is subject to restrictions set forth in subparagraph (C) (1) (ii) of the Rights in Technical Data and Computer Software Clause at DFARS 252.227-7013. Hewlett-Packard Company, 3000 Hanover Street, Palo Alto, CA 94304 U.S.A. Rights for non-DOD U.S. Government Departments and Agencies are as set forth in FAR 52.227-19(c) (1,2).

# **Printing History**

New editions are complete revisions of the manual. Many product updates and fixes do not require manual changes, and manual corrections may be done without accompanying product changes. Therefore, do not expect a one-to-one correspondence between product updates and manual revisions.

| Edition 5 | 64798-97004, April 1997    |

|-----------|----------------------------|

| Edition 4 | 64798-97003, December 1996 |

| Edition 3 | 64798-97002, November 1996 |

| Edition 2 | 64798-97001, August 1996   |

| Edition 1 | 64798-97000, July 1996     |

## Safety and Certification and Warranty

Safety information, and certification and warranty information can be found at the end of this manual on the pages before the back cover.

## The HP 64798C/E/F Emulator

#### Description

The Hewlett-Packard Model 64798C/E/F emulator supports the Motorola 6830x microprocessor family. The emulators and supported microprocessors include HP 64798C/MC68302, HP 64798E/MC68EN302, and HP 64798F/MC68LC302. In this manual, the HP emulators are referred to by Model Number 64798, and the Motorola microprocessors are referred to by MC6830x, except where specific information applies only to certain individual members of the emulator or microprocessor family.

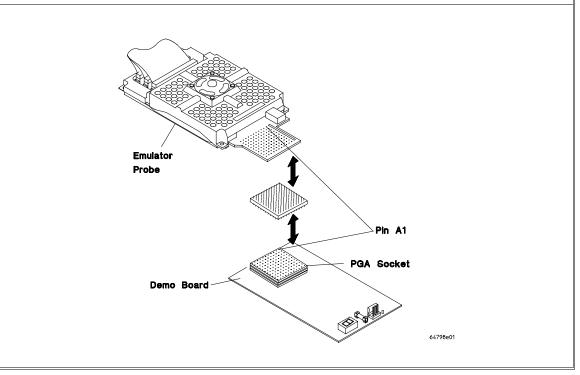

The emulator probe has a PGA-style connector. It can be plugged directly into the PGA connector on the demo board. Using optional accessories, it can be plugged into a 144-pin TQFP, a 132-pin PQFP, or a 100-pin TQFP target system. The 68302 emulator can also be plugged into a PGA connector on the target system using an optional transition socket. Find the list of probing accessories in the parts list in Chapter 7 and select the probe assembly kit or transition socket you need to connect this emulator to your 6830x target system.

Note that the PGA-style connector on the emulator probe is NOT compatible with the MC68302 PGA pinout. If you wish to connect the emulator to an MC68302 PGA pinout on your target system, use the PGA transition socket listed in chapter 7.

The emulator plugs into the modular HP 64700 instrumentation card cage and offers 64 channels of processor bus analysis with the HP 64794A or HP 64704A emulation-bus analyzer. A full 56 Kbytes of dual-port emulation memory is built into the emulator. Up to 8 megabytes of additional emulation memory may be installed on the probe. High performance download is achieved through the use of an optional LAN interface. An RS-232 port and a firmware-resident interface allow debugging of a target system at remote locations.

For software development, the HP AxCASE environment is available on SUN SPARCsystems and on HP workstations. This environment includes an ANSI standard C compiler, assembler/linker, a debugger, the HP Software Performance Analyzer that allows you to optimize your product software, and

the HP Branch Validator for test suite verification. The C compiler, assembler/linker, and debugger are also available for MS-DOS systems.

Language support is also available from several third-party vendors. This capability is provided through the HP 64700's ability to consume several industry standard output file formats.

#### **Features**

#### HP 64798 Emulator

- Active probe emulator; supports the fastest processor speeds currently available from Motorola. At the time this manual was printed, the emulator had been tested to the following processor speeds:

- 25 MHz for MC68302

- $\,25$  MHz for MC68EN302  $\,$

- -25 MHz for MC68LC302

- 5V operation (MC68302 and MC68EN302)

- 3.3V and 5V operation (MC68LC302)

- Supports the following clock speeds

- 8 MHz to 25 MHz (MC68302 and MC68EN302)

- 0 MHz to 25 MHz (MC68LC302)

- No wait states required

- Unlimited software breakpoints

- Symbolic support

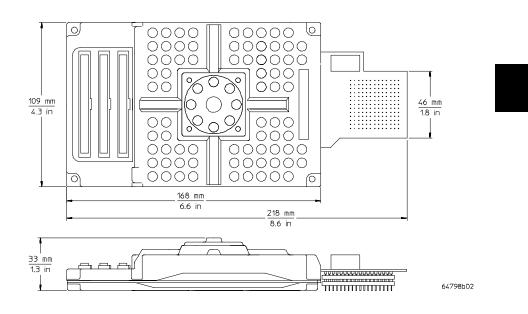

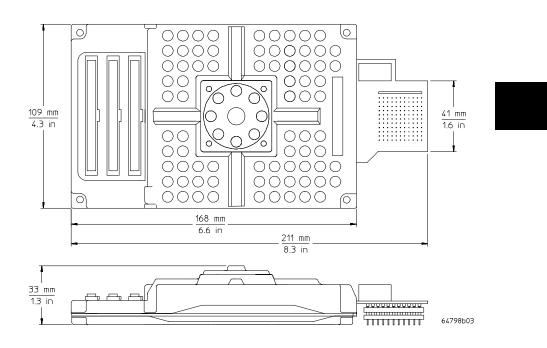

- 36-inch cable and 219-mm (8.6-inch) x 109 mm (4.3-inch) probe

- Background monitor

- Consumes IEEE-695, HP-OMF, Motorola S-Records, and Extended Tek Hex File formats directly. (Symbols are available with IEEE-695 and HP-OMF formats.)

- Multiprocessor emulation

- synchronous start of 32 emulation sessions

- cross triggerable from another emulator, logic analyzer, or oscilloscope

- Demo board and self-test module included

#### **Emulation-bus analyzer**

- 80-channel emulation-bus analyzer

- Post-processed trace with symbols

- Eight events, each consisting of address, status, and data comparators

- Events may be sequenced eight levels deep and can be used for complex trigger qualification and selective store

#### **Emulation memory**

- Up to 8 Mbytes of emulation memory

- 56 Kbytes of dual-ported emulation memory built in

- Mapping resolution is 256 bytes

- For MC68302, MC68EN302, and MC68LC302, no wait states required

# In This Book

This user's guide covers the Hewlett-Packard Model 64798 emulator for the MC6830x family of microprocessors. It is divided into the following parts:

Part 1, "Installation," shows you how to install and connect all of the emulator/analyzer hardware in the card cage, connect the card cage to a PC, and connect the emulator probe into the demo board and into your target system.

Chapter 4 in Part 1 leads you through a detailed procedure designed to help you connect the emulator into your target system and obtain satisfactory operation. Even if you have extensive emulator experience, you should read Chapter 4 to become familiar with problems that are specific to this processor and emulator.

Part 2, "Service," shows you how to install and update emulator/analyzer firmware, solve problems you may encounter while using the emulator/analyzer, and obtain replacement parts for the emulator/analyzer from Hewlett-Packard.

Part 3, "Terminal Interface Reference," introduces the interfaces available to use with the emulator/analyzer, and shows you how to use the terminal interface for the emulator/analyzer.

This manual replaces the Terminal Interface Reference which accompanied earlier HP emulators. For information on the Terminal Interface, see Part 3.

You should read the book *Concepts of Emulation and Analysis* when you have the chance to do so; it contains a good conceptual introduction to the emulation process, and also describes how an emulation monitor works. Another book, the *HP 64700 Card Cage Installation/Service Guide*, tells you more about installation and configuration of the HP 64700 Card Cage. If you have a problem with the emulator and don't understand how to fix it, a listing of HP Sales and Service offices is in the *Support Services Guide* in the back of this binder.

## Contents

#### Part 1 Installation Guide

#### **1** Preparing the Emulator

Preparing the Emulator 4

What you need 5

Antistatic Precautions 6

Installing a different emulator 6 Installing a different analyzer 6 Step 1. Install optional memory modules on Deep Analyzer card (if using the Deep Analyzer) 7 Step 2. Connect the emulator probe cables 9 Step 3. Install boards into the HP 64700 Card Cage 11 Step 4. Install emulation memory modules on emulator probe 24Step 5. Select a clock module 28Step 6. Connect the power cord 31

#### 2 Connecting to a Host Computer

Step 1: Choose a system configuration 34 Step 2: Connect the LAN cable 34 Step 3: Install host software 35 Step 4: Update emulator firmware 35 Step 5: Configure the LAN parameters 36 To configure LAN parameters using "ipconfig700" 37 To configure LAN parameters using the terminal interface 40 If "telnet" does not access the emulator 44

#### **3** Connecting to the Demo Board

Installation 46

Step 1. Connect the emulator probe to the demo target system47Step 2. Apply power to the HP 6470049Step 3. Verify the performance of the emulator50

#### 4 Connecting the Emulator to a Target System

Plugging The Emulator Into A Target System 52

Understanding an emulator 52 Target system design 52Buffering and AC specifications 53 DC specifications 54Target power 54Clock information 55Selecting a clock module 5860 Clock module circuits Clock module circuit details 62 Testing your custom crystal clock circuit 62 Connecting the emulator to an MC68302 target system 63 Connecting the emulator to an MC68EN302 target system 64E3437A Probing of 132-pin PQFP 65E5336A/E5338A Probing of 144-pin TQFP 66 E5367A Probing of target system PGA 67 Connecting the emulator to an MC68LC302 target system 68 E5356A Probing with MC68LC302 emulator 69 Verifying Operation Of The Emulator In Your Target System 70Additional equipment 70Probing 7172 Running the emulator configured like the processor To verify operation of the target system 73Interpreting the trace list 78Fixing timing problems 80 Installing the emulator in a target system without known good software 81 Installing Emulator Features 83 83 Evaluating the reset facilities Installing the background monitor 85 Resetting into the background monitor 85 Testing memory accesses with the background monitor 86 Running a program from the background monitor 87 Breaking into the background monitor 88 Exiting the background monitor 89 Software breakpoint entry into the background monitor 90 Stepping with the background monitor 91 Driving background cycles to the target 93Freezing microprocessor peripherals during background cycles 93 Emulation memory 94Expanding emulation memory 9494 Mapping emulation memory Accessing emulation memory 95 Selecting 8-bit or 16-bit emulation memory 95Function of Emulation Copy of Processor Registers 95Configuring the emulator 96 User Convenience 96 Completing emulation memory cycles with target DTACK 97

#### Part 2 Service

#### 5 Installing/Updating HP 64700 Firmware

Installing/Updating HP 64700 Firmware 102 Updating the firmware using a workstation 103 Updating the firmware using a PC 103Step 1. Connect the HP 64700 card cage to your PC 104 Step 2. Install the firmware update utility 106 Step 3: Run "progflash" to update emulator firmware 108 If the "progflash" routine won't work 111 Step 4. Verify emulator performance 111

#### 6 Solving Problems

To verify the performance of the emulator 115What is pv doing to the emulator? 117 Troubleshooting 118 To ensure software compatibility 118 To display the emulator status 120 To check the version of the terminal interface software 120 If the performance verification reports massive pv failures 121 If the emulator appears to be malfunctioning 121 If you suspect the emulator is broken 121 If you have RS-232 connection problems 122 If you see "Unable to break" when trying to initialize the graphical user interface 124 If emulation memory behavior is erratic 124 If you're having problems with DMA 124If the analyzer triggers on a program address when it should not 125If you see unexplained states in the trace list 126 If you see exclamation marks "!" in count columns of the trace lists 127 If you see negative time or state counts in trace lists 127 If you do not see the counter overflow indication "!" where you expected to see it in a trace list 128 If the instrument requires cleaning 128

#### 7 Parts List

Parts List 130 What is an exchange part? 130

#### Part 3 Terminal Interface Reference

#### 8 Using the Terminal Interface

When to Use the Terminal Interface138Learning About the Terminal Interface139To start the terminal interface139To view a list of available commands140To view help on individual commands142To view help on command syntax142Graphical Interfaces143

Why use a graphical interface? 143

#### 9 MC68302/MC68EN302 Specifications and Characteristics

Processor compatibility 146 Electrical 146 HP 64798C/E maximum ratings 147 HP 64798C/E DC electrical characteristics 148 HP 64798C/E AC Electrical Specifications 152Clock Timing 153IMP Bus Master Cycles 154 DMA 161 External Master Internal Asynchronous Read/Write Cycles 163External Master Internal Synchronous Read/Write Cycles 165Internal Master Internal Read/Write Cycles 167Chip Select Timing Internal Master 168Chip Select Timing External Master 171Parallel I/O 172Interrupts 173

Contents

Timers174Physical MC68302/MC68EN302175Environmental176BNC, labeled TRIGGER IN/OUT177Communications177

#### 10 MC68LC302 Specifications and Characteristics

Processor compatibility 190 Electrical 190 HP 64798F maximum ratings 191 HP 64798F DC electrical characteristics 192HP 64798F AC Electrical Specifications 196Clock Timing 197IMP Bus Master Cycles 198 DMA 202 External Master Internal Asynchronous Read/Write Cycles 204External Master Internal Synchronous Read/Write Cycles 205 Chip Select Timing Internal Master 207Chip Select Timing External Master 209 Parallel I/O 210 Interrupts 211 212 Timers Physical 213Environmental 215BNC, labeled TRIGGER IN/OUT 216 Communications 216

#### Glossary

Index

Part 1

Installation Guide

1

# Preparing the Emulator

How to connect the emulator probe and power cord.

## Preparing the Emulator

This chapter shows you how to install the emulation and analysis hardware in the emulator card cage.

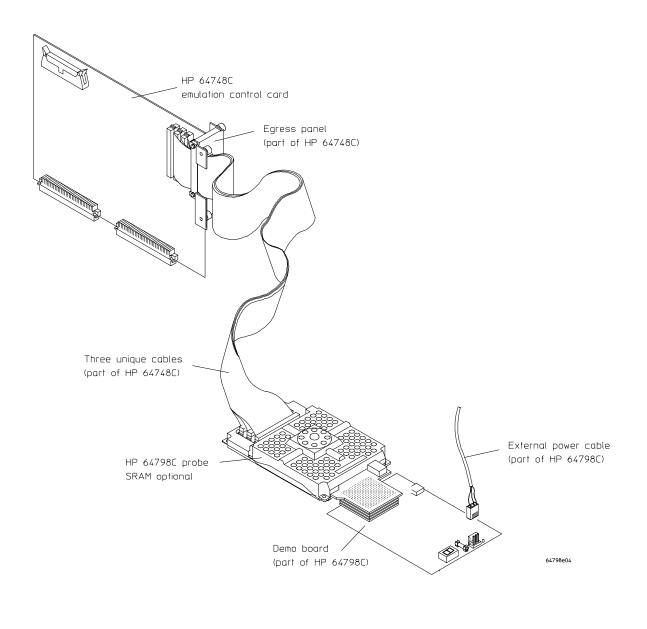

The installation tasks are described in the following steps:

- 1 Install optional memory modules on the deep analyzer card, if desired.

- 2 Connect the HP 64798 emulator probe to the HP 64748C emulator control card.

- 3 Install cards in the HP 64700 card cage.

- 4 Install emulation memory modules on the emulator probe.

- 5 Installing optional clock modules.

- 6 Connect a power cord to the HP 64700 Card Cage.

### What you need

#### **Equipment supplied**

The minimum system contains:

- HP 64798 MC6830x PGA Emulator Probe

- Demo target system (shipped with the emulator probe).

- HP 64748C Emulation Control card.

- HP 64794A/C/D Emulation-Bus Analyzer (deep analyzer) card, or HP 64704A 80-channel Emulation-Bus Analyzer (1K analyzer) card.

- 80-Channel Analyzer Extender Ribbon Cable.

- HP 64700A or HP 64700B Card Cage.

#### Optional parts are:

- HP 64171A/64172A 256-Kbyte Memory Modules for additional memory depth.

- HP 64171B/64172B 1-Mbyte Memory Modules for additional memory depth.

- HP 64173A 4-Mbyte Memory Modules for additional memory depth.

- HP 64708A Software Performance Analyzer.

- HP 64701A LAN Interface card (HP 64700A only).

- Probing accessories for connecting to a target system (see Chapter 7).

#### Equipment and tools needed

In order to install and use the MC6830x emulation system, you need:

- Probe assembly kit for connecting the emulator probe to a target system (not needed for connecting to the demo board). See Chapter 7.

- Flat-blade screwdriver with shaft at least 5 inches long (13 mm approx).

- Torx T-10 screwdriver (if installing the optional LAN card for the HP 64700A).

The illustrations in this manual show the HP 64700B Card Cage. The locations of some components may be slightly different if you are using an HP 64700A Card Cage.

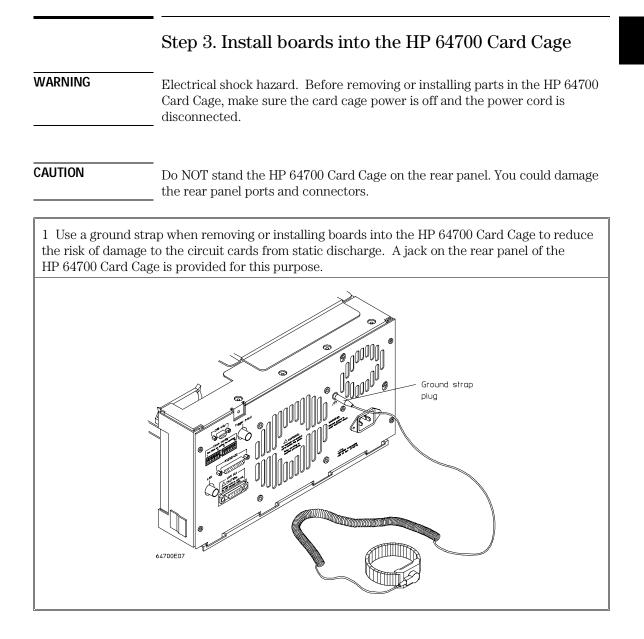

## Antistatic Precautions

Printed-circuit boards contain electrical components that are easily damaged by small amounts of static electricity. To avoid damage to the emulator boards, follow these guidelines:

- If possible, work at a static-free workstation.

- Handle the boards only by the edges; do not touch components or traces.

- Use a grounding wrist strap that is connected to the HP 64700 chassis.

#### Installing a different emulator

If you already have an HP 64700-Series Card Cage and want to remove the existing emulator and insert an HP 64798 emulator in its place, the HP 64700-Series generic firmware and analyzer firmware may NOT be compatible, and the software will indicate incompatibility. In this event, you must purchase a Flash EPROM board to update the firmware. Instructions for installing this board and programming it from a PC or HP 9000 are provided in the HP 64700 Card Cage Installation/Service manual. Instructions for installing and updating emulator firmware are covered in Chapter 5, "Installing/Updating Emulator Firmware" in this manual.

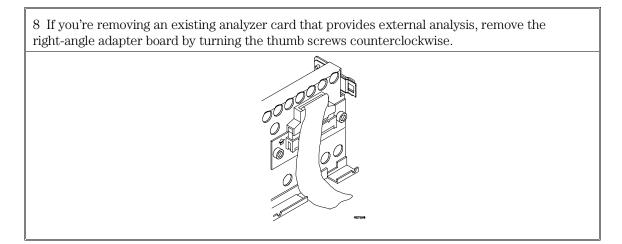

#### Installing a different analyzer

If you already have an HP 64700-Series Card Cage and want to remove the 1K analyzer and install the deep analyzer in its place, the analyzer firmware will be updated by your installation because the analyzer firmware is contained on the analyzer card.

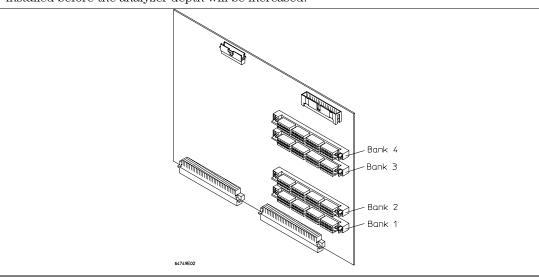

## Step 1. Install optional memory modules on Deep Analyzer card (if using the Deep Analyzer)

#### **Observe antistatic precautions**

With no optional memory modules installed on the deep analyzer card, the trace memory depth is 8K. If you are going to use the deep analyzer with this default trace memory depth, skip this step.

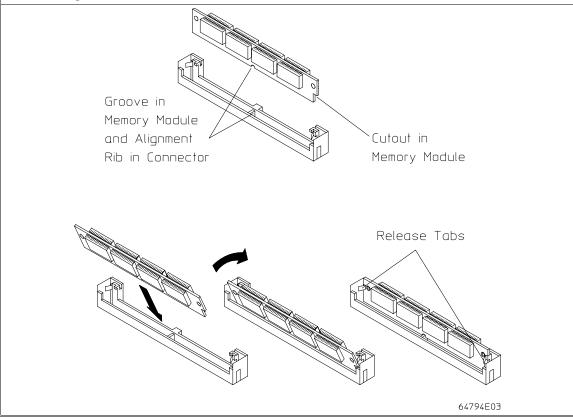

1 Determine the placement of the optional memory modules. Two types of modules may be installed: 256-Kbyte (HP 64172A), and 1-Mbyte (HP 64172B). Either module type may be installed in the banks on the analyzer card. Do not use HP 64171A/B or HP 64173A memory modules; they are too slow.

If you install no memory modules, the deep analyzer will have 8K maximum memory depth. If you install four 256-Kbyte memory modules, the analyzer will have 64K maximum memory depth.

If you install four 1-M byte memory modules, the analyzer will have 256K maximum memory depth.

If you install a combination of 256-Kbyte memory modules and 1-Mbyte memory modules, the analyzer will have 64K maximum memory depth. All four connectors must have memory modules installed before the analyzer depth will be increased.

#### Chapter 1: Preparing the Emulator Step 1. Install optional memory modules on Deep Analyzer card (if using the Deep Analyzer)

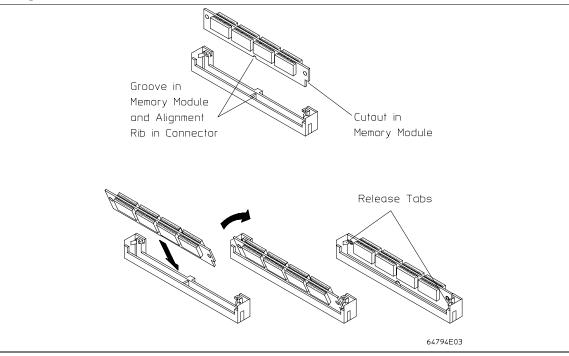

2 To ensure correct installation of optional memory modules on the deep analyzer card, there is a cutout at one end of the memory modules so they can only be installed the correct way.

To install a memory module:

Align the groove in the memory module with the alignment rib in the connector.

Align the cutout in the memory module with the projection in the connector.

Place the memory module into the connector groove at an angle.

Firmly press the memory module into the connector and make sure it is completely seated.

Rotate the memory module forward so that the pegs on the connector fit into the holes on the memory module.

Make sure the release tabs at each end of the connector snap around the memory module to hold it in place.

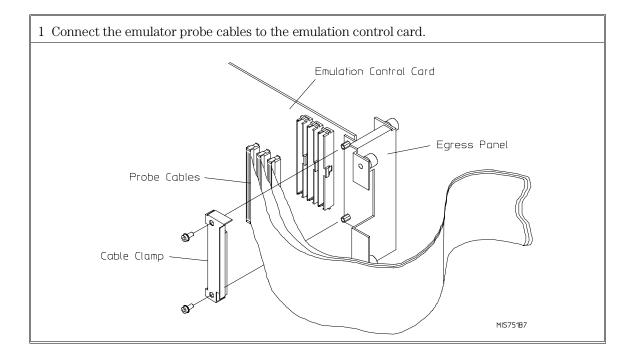

### Step 2. Connect the emulator probe cables

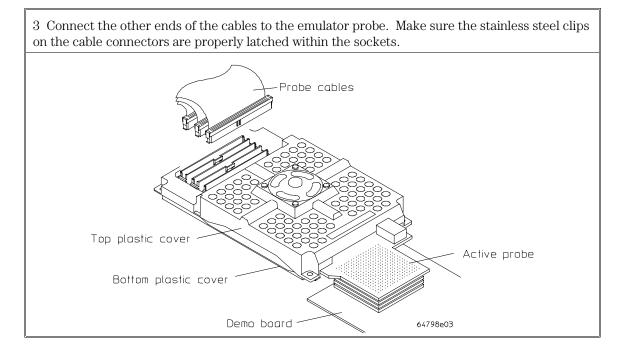

Three ribbon cables connect the HP  $64748\mathrm{C}$  emulation control card to the HP 64798 emulator probe.

The shortest cable connects from J1 of the emulation control card to J3 of the emulator probe. The medium length cable connects from J2 of the emulation control card to J2 of the emulator probe. The longest cable connects from J3 of the emulation control card to J1 of the emulator probe.

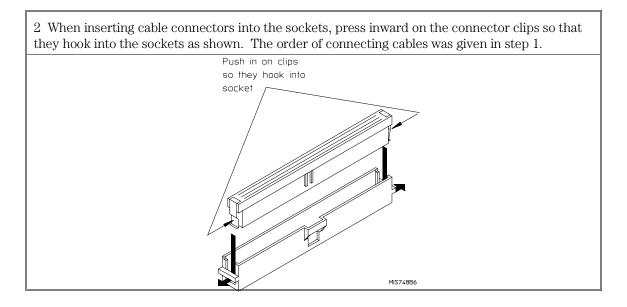

Make sure the cable connectors are seated. There are stainless steel clips on the cable connectors; these must be properly latched inside the sockets. Otherwise, the cables will work loose and you will see erratic operation. See illustration next page (step 2).

#### Chapter 1: Preparing the Emulator Step 2. Connect the emulator probe cables

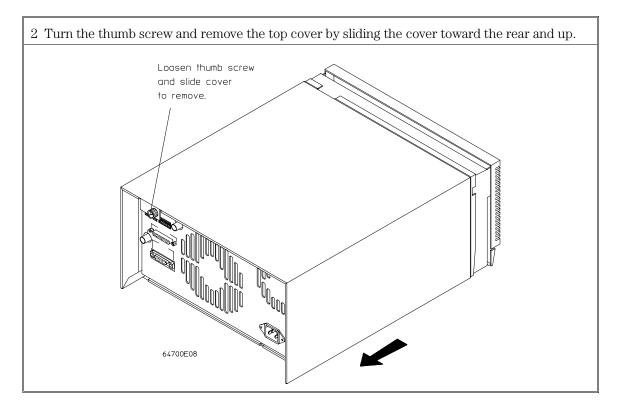

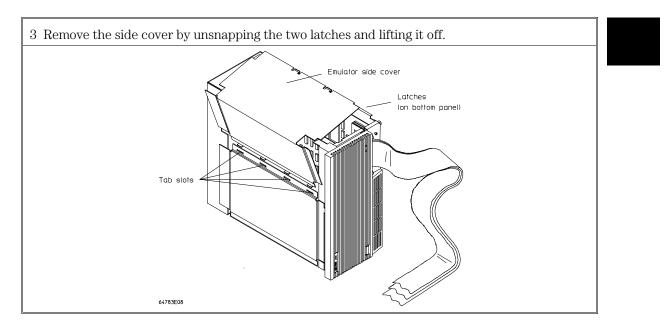

#### Chapter 1: Preparing the Emulator Step 3. Install boards into the HP 64700 Card Cage

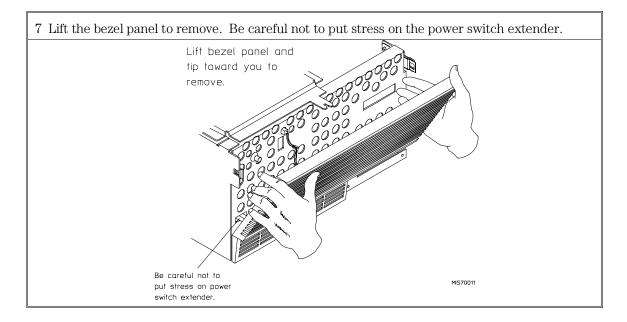

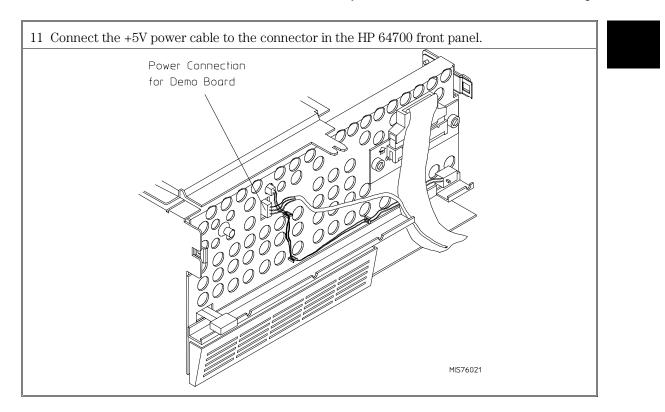

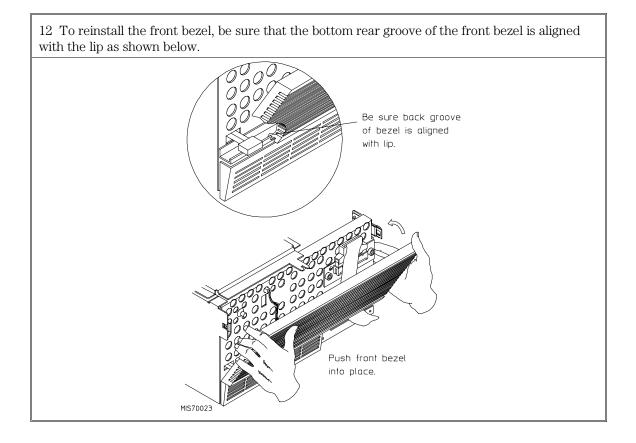

6 Insert a screw driver into the third slot of the right side of the front bezel, push to release catch, and pull the right side of the bezel about one-half inch away from the front of the HP 64700. Then, do the same thing on the left side of the bezel. When both sides are released, pull the bezel toward you approximately 2 inches. Be careful because the plastic ears are easily broken on the front bezel. Be careful because the plastic ears are easily broken on the front bezel. Insert screw driver into third slot of front bezel, push to release catch and pull bezel toward you. Insert screw driver into third slot of front bezel, push to release catch and pull bezel toward you.

#### Chapter 1: Preparing the Emulator Step 3. Install boards into the HP 64700 Card Cage

Do not remove the system control board. This board is used in all HP 64700 emulation and analysis systems.

#### Chapter 1: Preparing the Emulator Step 3. Install boards into the HP 64700 Card Cage

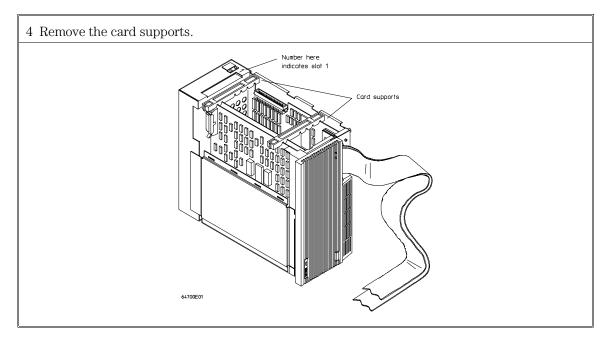

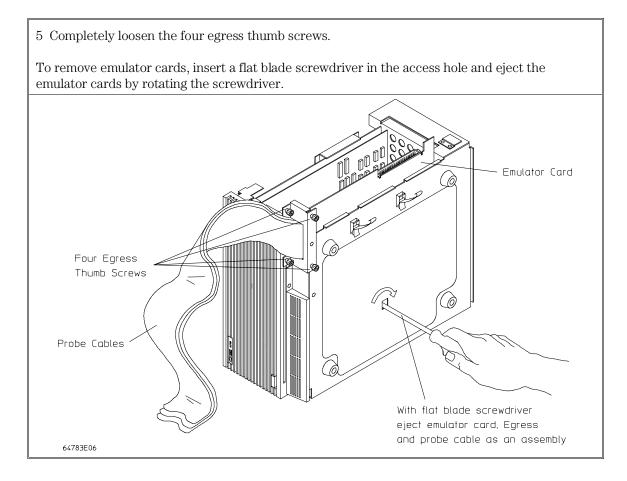

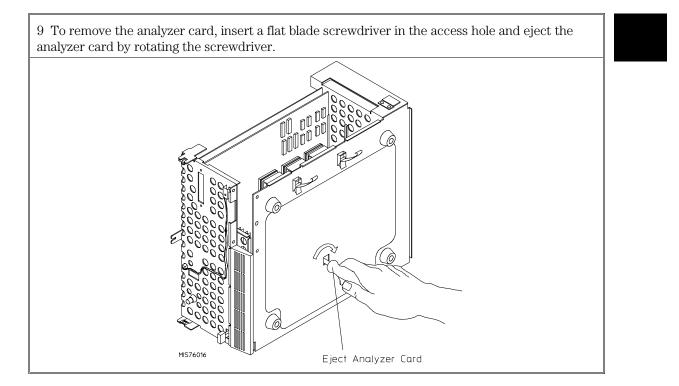

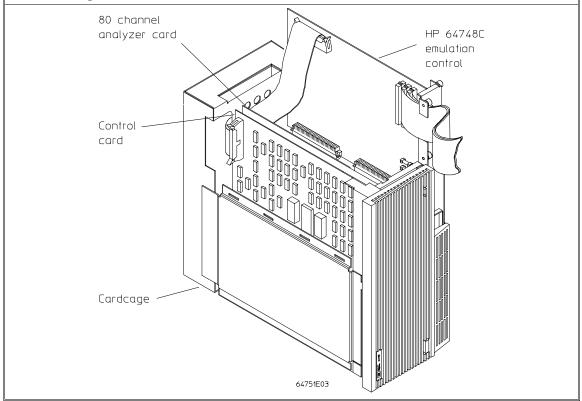

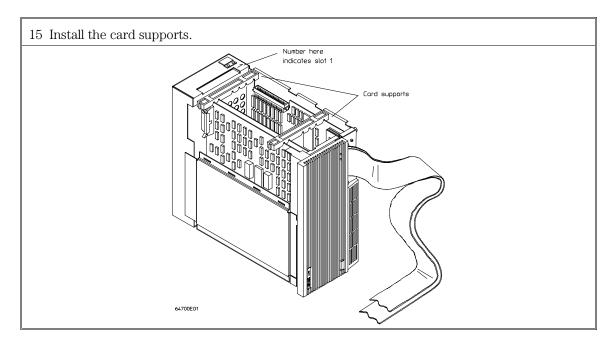

10 Install the analyzer and emulation control cards. The analyzer is installed in the slot next to the system control card. The emulation control card is installed in the second slot from the bottom of the card cage. The software performance analyzer card may occupy any slot between the emulation-bus analyzer and the emulation control card. These cards are identified with labels that show their model numbers and serial numbers. Note that components on the analyzer card face the opposite direction to the other cards.

To install a card, insert it into the plastic guides. Make sure the connectors are properly aligned; then, press the card into the mother board socket. Ensure that each card is seated all the way into its socket. If the cards can be removed with your fingers, the cards are NOT seated all the way into the mother board sockets.

Attach the ribbon cable from the emulation control card to the analyzer card, and to the software performance analyzer, if installed. Tighten the thumbscrews that hold the emulation control card to the cardcage frame.

# Chapter 1: Preparing the Emulator Step 3. Install boards into the HP 64700 Card Cage

#### Chapter 1: Preparing the Emulator Step 3. Install boards into the HP 64700 Card Cage

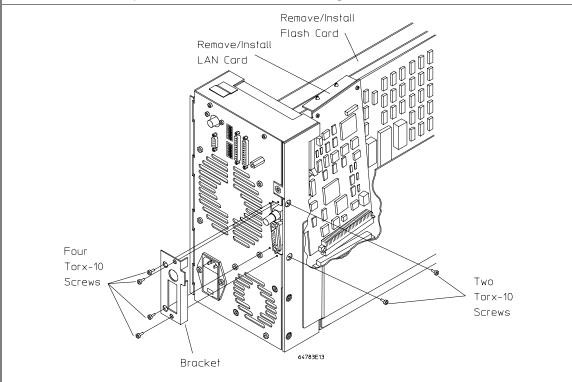

13 This step applies only to the HP 64700A. The HP 64700B has a built-in LAN interface.

Before you install the LAN card, you must remove the rear panel cover plate that is replaced by the bracket shown in the figure below.

To install the LAN card, position the BNC and 15-pin connectors of the LAN card through the openings in the rear panel, press the card into the mother board socket, secure the card with the two Torx T-10 screws, and mount the bracket to the rear panel with the four Torx T-10 screws.

14 *This step applies only to the HP 64700A*. If you wish to install the flash card (used for updating firmware, see Chapter 5), refer to the diagram above. Install the flash card in any available slot between the 80-channel analyzer card and the HP 64748C control card in the cardcage. Insert the flash card in the plastic guides. Make sure the connectors are properly aligned. Then press the card all the way into the mother board sockets.

#### Chapter 1: Preparing the Emulator Step 3. Install boards into the HP 64700 Card Cage

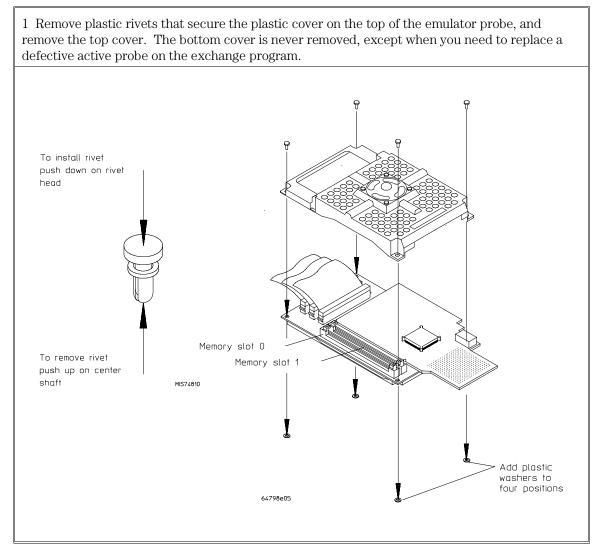

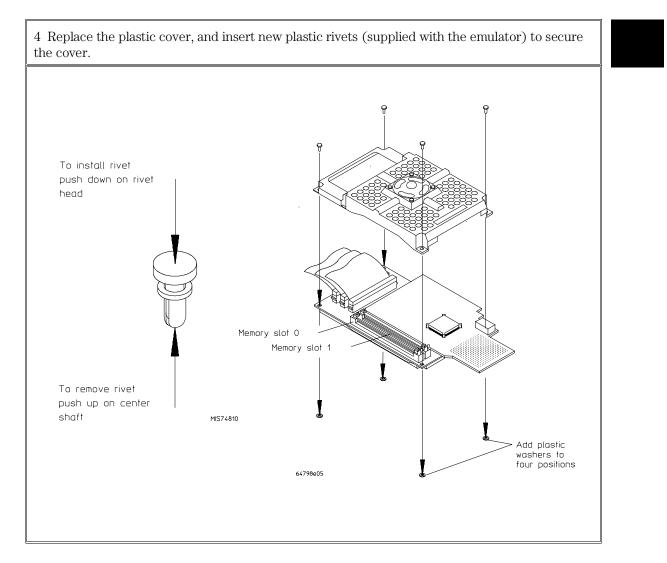

## Step 4. Install emulation memory modules on emulator probe

#### **Observe antistatic precautions**

2 Emulation memory modules (SIMM) can be installed in either or both memory slots on the emulator probe. The emulator software will automatically arrange the most efficient use of SIMM hardware when mapping memory. See "How memory is allocated in the Emulation Probe," below.

Three types of SIMMs may be installed: 256 Kbyte (HP 64171A/64172A), 1 Mbyte (HP 64171B/64172B), and 4 Mbyte (HP 64173A).

If you need new rivets or washers to complete the installation procedure, refer to Chapter 7, "Parts List," for the part number of the Plastic Rivets Kit.

| How memory is allocated in the Emulation Probe            |                                                         |                                                                                  |                                                             |  |  |

|-----------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|

| Number of emulation<br>memory modules<br>(SIMM) installed | Blocks of SIMM<br>available for mapping<br>(Notes 1, 2) | Blocks of built-in,<br>dual-port memory<br>available for mapping<br>(Notes 3, 4) | Maximum number of<br>memory blocks<br>available for mapping |  |  |

| 0                                                         | 0                                                       | 7                                                                                | 7                                                           |  |  |

| 1                                                         | 4                                                       | 7 (Note 5)                                                                       | 8                                                           |  |  |

| 2 (Notes 6, 7)                                            | 8                                                       | 7 (Note 5)                                                                       | 8                                                           |  |  |

Notes:

1. SIMM hardware is not dual-port, but built-in memory is dual-port.

2. Each SIMM is divided into four equal blocks by emulator software. Each block is 1/4 the size of the associated SIMM.

- 3. Built-in emulation memory contains seven 8-Kbyte, dual-port blocks.

- 4. 8-Kbyte blocks of built-in memory can be substituted for SIMM blocks using a command such as, "map 1000..1fff eram dp."

- 5. By default, the emulator maps memory to blocks of SIMM before mapping memory to the built-in, 8-Kbyte, dual-port blocks. To override the default, include "dp" in your map command. See Note 4.

6. Different size SIMMs can be installed in either memory slot.

7. The emulator automatically selects the most appropriate block size to contain each mapped address range.

#### Chapter 1: Preparing the Emulator Step 4. Install emulation memory modules on emulator probe

3 Install emulation memory modules on the emulator probe. There is a cutout at one end of the memory modules so they can only be installed the correct way.

To install a memory module:

- 1 Align the groove in the memory module with the alignment rib in the connector.

- 2 Align the cutout in the memory module with the projection in the connector.

- 3 Place the memory module into the connector groove at an angle.

- 4 Firmly press the memory module into the connector and make sure it is completely seated.

- 5 Rotate the memory module to the vertical position so that the pegs on the connector fit into the holes on the memory module.

- 6 Make sure the release tabs at each end of the connector snap around the memory module to hold it in place.

## Chapter 1: Preparing the Emulator Step 4. Install emulation memory modules on emulator probe

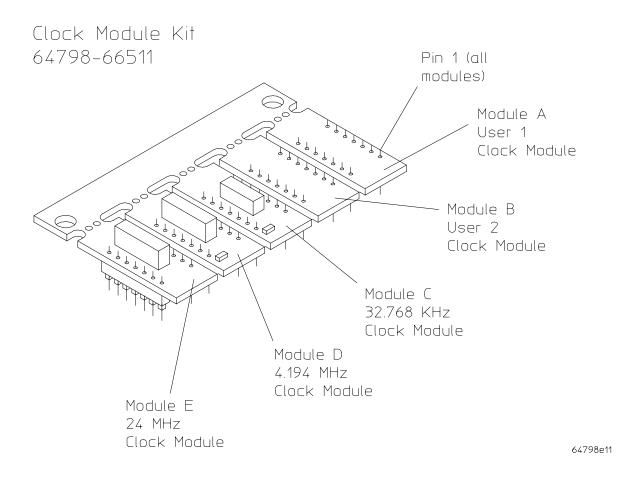

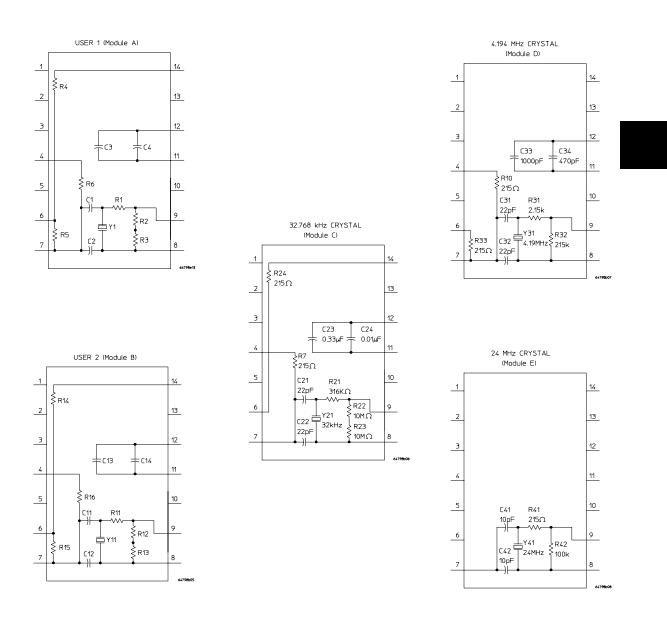

#### Step 5. Select a clock module

The MC6830x emulator can operate with either an external clock (supplied from the target system), or an internal clock (supplied from a module installed on the emulator probe clock socket). In addition, the MC6830x processors can operate from either an oscillator or a crystal. The table below will help you select the clock source that is appropriate for the microprocessor and clock mode being emulated.

| Microprocessor and                   | Clock source for emulator                                                                           |                                                                                                                                              |  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Clock Mode                           | Internal<br>cf clk = int                                                                            | External<br>cf clk = ext                                                                                                                     |  |

| 68302 and 68EN302 with<br>oscillator | oscillator module:<br>20 MHz supplied by HP or<br>8-25 MHz supplied by user                         | Any oscillator or crystal<br>module. This provides a<br>working internal clock which<br>must be detected during<br>interface initialization. |  |

| 68302 and 68EN302 with crystal       | 24 MHz (Module E), or<br>User 1 (Module A), or<br>User 2 (Module B)                                 | Not supported.                                                                                                                               |  |

| 68LC302 with oscillator              | oscillator module:<br>20 MHz supplied by HP or<br>0-25 MHz supplied by user                         | Any oscillator or crystal<br>module. This provides a<br>working internal clock which<br>must be detected during<br>interface initialization. |  |

| 68LC302 with crystal                 | 32.768 kHz (Module C), or<br>4.194 MHz (Module D), or<br>User 1 (Module A), or<br>User 2 (Module B) | Not supported.                                                                                                                               |  |

Refer to Chapter 4 for details of making the choices described in the table above. If you wish to develop your own clock source with the User 1 or User 2 modules, example schematics are shown in Chapter 4.

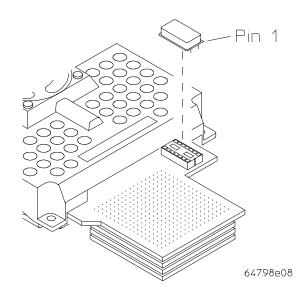

When using the internal clock, you can install either an oscillator or a crystal in the emulator probe clock socket. The diagram below shows how to install an internal clock module.

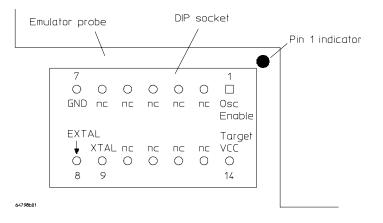

The emulator probe clock socket is a 14-pin DIP socket located on the top of the emulator probe. A standard 14-pin DIP type CMOS oscillator operating within specifications appropriate for your emulator (see table on previous page) may be installed in the clock socket. Pin 1 provides Oscillator Enable (active high) for oscillators that need it. A white dot beside the clock socket indicates pin 1.

The MC6830x emulator is shipped with a 20-MHz CMOS oscillator, packaged separately. You must install an internal clock module when running the emulator performance verification (pv).

## Chapter 1: Preparing the Emulator **Step 5. Select a clock module**

Five clock modules are available on the HP Clock Module Kit, which is supplied with the MC6830x emulator. Additional clock module kits can be ordered from Hewlett-Packard for emulator support. To use one of these modules, break off the desired module from the clock module kit and install it in the emulator probe clock socket. Be careful to align pin 1 correctly.

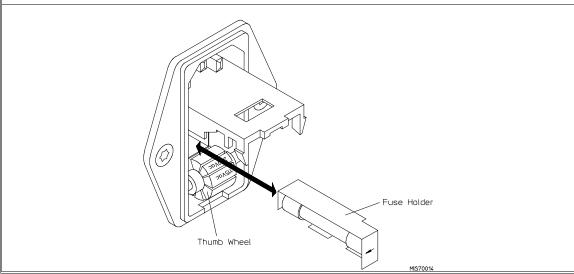

#### Step 6. Connect the power cord

The HP 64700B automatically selects the 115 Vac or 220 Vac range. In the 115 Vac range, the HP 64700B will draw a maximum of 345 W and 520 VA. In the 220 Vac range, the HP 64700B will draw a maximum of 335 W and 600 VA.

If you have the emulator installed in an HP 64700A card cage, select the line voltage using a thumb-wheel switch inside the power control module on the rear panel of the card cage. The input frequency must be in the range of 48 to 66 Hz. At 115 Vac, the emulator will draw a maximum of 3.0 A. At 220 Vac, it will draw a maximum of 1.5 A.

The HP 64700 is shipped from the factory with a power cable appropriate for your country. You should verify that you have the correct power cable for installation.

If the cable you received is not appropriate for your electrical power outlet type, contact your Hewlett-Packard sales and service office.

Chapter 1: Preparing the Emulator **Step 6. Connect the power cord**

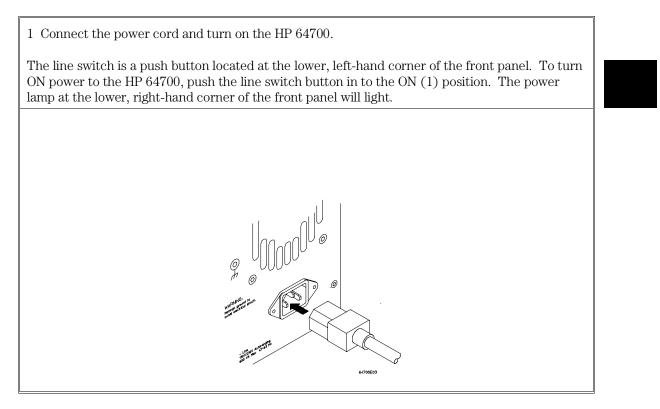

$1\,$  Connect the power cord and turn on the HP 64700.

The line switch is a pushbutton located at the lower, left-hand corner of the front panel. To turn ON power to the HP 64700, push the line switch button in to the ON (1) position. The power lamp at the lower, right-hand corner of the front panel will light.

## Connecting to a Host Computer

How to connect the emulator to a PC or terminal.

As you follow the steps in this chapter, you will need to refer to the 64700 Card Cage Installation/Service Guide.

#### Step 1: Choose a system configuration

- 1 Decide how you will connect the emulator to your host computer. Refer to the "Concepts" chapter in the 64700 Card Cage Installation/Service Guide.

- **2** If you will be using a LAN connection, continue with the steps in this chapter.

If you will be using a serial connection, refer to the information in the 64700 *Card Cage Installation/Service Guide*; you may skip the rest of this chapter.

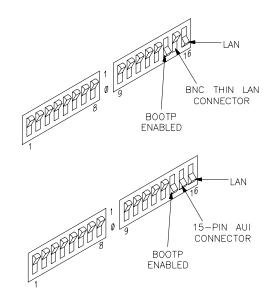

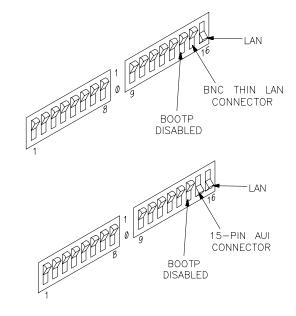

#### Step 2: Connect the LAN cable

• Connect the LAN to either the BNC connector or the 15-pin AUI connector.

The card cage can communicate with computers on an IEEE 802.3 or Ethernet Local Area Network. (If you have a 64700A card cage, you need the HP 64701A LAN card to connect to a LAN.) You can use either of two LAN connectors:

- A BNC connector that can be directly connected to a ThinLAN (HP's implementation of IEEE 802.3 Type 10BASE2) cable. The card cage provides the functional equivalent of a Medium Attachment Unit (MAU) for ThinLAN.

- A 15-pin connector for an Attachment Unit Interface (AUI) cable. The AUI cable allows you to connect to an off-board MAU for ThinLAN, a ThickLAN (HP's implementation of IEEE 802.3 Type 10BASE5)

#### Chapter 2: Connecting to a Host Computer Step 3: Install host software

connection, or to a Pod for a StarLAN 10 (HP's implementation of IEEE 802.3 Type 10BASE-T) connection.

CAUTIONCORRUPTED DATA! The LAN connection to the BNC will maintain software<br/>integrity and can maintain communication when subjected to low levels of<br/>Electrostatic Discharge (ESD) directly to the LAN connector.

When operating in an environment where ESD pulses are in excess of 2500 volts, using a ThinMAU adapter (instead of a direct connection) is more reliable and less susceptible to data corruption from ESD to the LAN cable.

Use either the BNC or the AUI connector. Do NOT use both. The LAN interface will not work with both connected at the same time.

#### Step 3: Install host software

- 1 If you have not already done so, install the LAN software on your host computer.

- **2** If you are using a UNIX-based workstation, install the interface software now.

HP supplies the ipconfig700 command as part of the HP B1471 64700 Operating Environment software. This command will greatly simplify the task of configuring the LAN connection.

#### Step 4: Update emulator firmware

If you did not receive your HP 64700 Card Cage and HP 64798 Emulator together (perhaps you are installing your HP 64798 Emulator in a card cage that had a different emulator installed in it), update the emulator firmware according to the steps in Chapter 5, "Installing/Updating Emulator Firmware."

#### Step 5: Configure the LAN parameters

- If you are using a UNIX-based workstation and you have installed the **ipconfig700** command, see "To configure LAN parameters using 'ipconfig700'" in this chapter.

- If you are using an HP-UX workstation, and you have not installed the **ipconfig700** command, see "To configure LAN parameters using BOOTP" in the *64700 Card Cage Installation/Service Guide*.

- If you are using the HP Real-Time C interface on a PC, see the instructions in your Real-Time C Debugger interface manual.

- Otherwise, see "To configure LAN parameters using the terminal interface" in this chapter.

#### To configure LAN parameters using "ipconfig700"

If you are using an HP 9000 Series 300/400/700 computer or Sun SPARCsystem computer and you have installed the HP B1471 64700 Operating Environment software, you can configure the LAN parameters with the ipconfig700 command.

The ipconfig700 command sets the Internet Address (IP address), Gateway Address, and Subnet Mask on the card cage LAN interface. An Internet Address (also known as an IP address) must be configured for the card cage before a network interface connection can be made.

The ipconfig700 command cannot be used if your system has a bootp daemon running. If this is the case, use BOOTP to configure LAN parameters.

The following steps need to be taken when configuring the network parameters.

- 1 Connect the card cage to your network. This connection can be made by using either the 15 Pin AUI connector or the BNC connector.

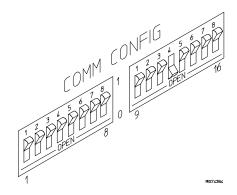

- 2 Set the rear panel dip switches to indicate the type of connection that is to be made.

#### Chapter 2: Connecting to a Host Computer To configure LAN parameters using "ipconfig700"

Switch 16 must be set to one (1) indicating that a LAN connection is being made.

Switch 15 should be zero (0) if you are connecting up to the BNC connector or set to one (1) if a 15 pin AUI connection is made.

Switch 14 must be set to one (1) to prepare for the receiving of the network parameters.

Set all other switches to zero (0).

- **3** Turn ON power to the emulator card cage.

- 4 Become the root user on the host computer.

## 5 Enter the **ipconfig700** -l <link> -i <internet> [-g <gateway>] [-s <subnet>] command.

The ipconfig700 parameters are:

| -l <link/>               | The Link Level Address is entered as 12 character hex<br>ASCII address. This address is configured in each LAN<br>interface shipped from the factory. This address is printed<br>on the rear panel of the card cage. For example,<br>08000F090B30 is a link level address.                                                                                                                                                                                     |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -i <internet></internet> | The Internet Address must be obtained from your Local<br>System Administrator. The value is entered in integer dot<br>notation. For example, 192.35.12.6 is an Internet Address.                                                                                                                                                                                                                                                                               |

| -g <gateway></gateway>   | The Gateway Address is also an Internet address and is<br>entered in integer dot notation. This entry is optional and<br>will default to 0.0.0.0, meaning all connections are to be<br>made on the local network or subnet. If connections are to<br>be made to workstations on other networks or subnets, this<br>address must be set to the address of the gateway<br>machine. The gateway address must be obtained from<br>your local system administrator. |

| -s <subnet></subnet>     | The Subnet Mask is also entered in integer dot notation.<br>This entry is optional and will default to 0.0.0.0. The                                                                                                                                                                                                                                                                                                                                            |

#### Chapter 2: Connecting to a Host Computer To configure LAN parameters using "ipconfig700"

default is valid only on networks that are not subnetted. (A network is subnetted if the host portion of the Internet address is further partitioned into a subnet portion and a host portion.) If the network is subnetted, a subnet mask is required in order for the emulator to work correctly. The subnet mask should be set to all "1"s in the bits which correspond to the network and subnet portions of the Internet address and all "0"s for the host portion. The subnet mask must be obtained from your local system administrator.

If the ipconfig700 command is entered without any options, the program interactively prompts for the necessary information.

If the Link Level Address on the rear panel of your card cage read 08000F090F30, and your system administrator gave you the Internet Address 192.35.12.6, you could enter the following command:

\$ ipconfig700 -1 08000F090B30 -i 192.35.12.6 <RETURN>

Since no Gateway Address or Subnet Mask was entered, these values would default to 0.0.0.0. When the Internet Address is successfully programmed, ipconfig700 will ask the emulator to display its version information.

- **6** Set switch 14 back to zero (0). Do this so the next time power is cycled on the emulator it will not enter a state waiting for network parameters.

- 7 Verify your emulator is now active and on the network by issuing a **telnet** to the Internet Address. For example:

\$ telnet 192.35.12.6 <RETURN>

This connection will give you access to the emulator's built-in terminal interface. To exit from this telnet session, type <CTRL>d at the emulator prompt.

Once you have entered an Internet Address, and you want to change it to a different number, the best way to accomplish this is to telnet to the emulator and use the terminal interface lan command to make the change.

To configure LAN parameters using the terminal interface

- 1 Set all of the rear panel switches to the down position. This will set the serial port (Port A on a 64700A and the RS232/422 port on a 64700B card cage) to 9600 baud and DCE.

- **2** Connect an ASCII terminal to the serial port with a 25-pin RS-232 cable.

You can also connect to a computer's RS-232 port and use a terminal emulation program on the computer. Refer to the "Connecting the HP 64700 Using RS-232/RS-422" chapter in the 64700 Card Cage Installation/Service Guide.

- **3** Turn ON the emulator card cage. Press the terminal's <RETURN> key a couple times. You should see the "R>" prompt.

- 4 Display the current LAN configuration values by entering the **lan** command:

```

R>lan

lan -i 0.0.0.0

lan -g 0.0.0.0

lan -s 0.0.0

lan -p 6470

Ethernet Address : 08000903212f

```

Note the Ethernet Address, also known as the link-level address. This address is preassigned at the factory, and is printed on the rear panel.

## 5 Enter the lan -i <internet> [-g <gateway>] [-s <subnet>] [-p <port>] command.

The lan command parameters are:

-i <internet> The Internet Address must be obtained from your local system administrator. The value is entered in integer dot notation. For example, 192.35.12.6 is an Internet Address.

### Chapter 2: Connecting to a Host Computer **To configure LAN parameters using the terminal interface**

- -g <gateway> The Gateway Address is also an Internet Address and is entered in integer dot notation. This entry is optional and will default to 0.0.0.0, meaning all connections are to be made on the local network or subnet. If connections are to be made to workstations on other networks or subnets, this address must be set to the address of the gateway machine. The gateway address must be obtained from your local system administrator.

- -s <subnet> The Subnet Mask (in integer dot notation) is optional and only available when using the HP 64700A. It defaults to 0.0.0.0. The default is valid only on networks that are not subnetted. (A network is subnetted if the host portion of the Internet address is further partitioned into a subnet portion and a host portion.) If the network is subnetted, a subnet mask is required in order for the emulator to work correctly. The subnet mask should be set to all 1s in the bits which correspond to the network and subnet portions of the Internet address and all 0s for the host portion. The subnet mask must be obtained from your system administrator.

-p <port> This changes the base TCP service port number. The host computer interfaces communicate with the emulator through two TCP service ports. The default base port number is 6470. The second port has the next higher number (default 6471). If you change the base port, the new value must also be entered in the /etc/services file on the host computer. For example, you could modify the line:

hp64700 6470/tcp

The default numbers (6470, 6471) can be changed if they conflict with some other product on your network. TCP service port numbers must be greater than 1024.

#### Chapter 2: Connecting to a Host Computer To configure LAN parameters using the terminal interface

For example, to assign an Internet Address of 192.6.94.2 to the emulator, enter the following command:

R>lan -i 192.6.94.2 <RETURN>

The Internet Address and any other LAN parameters you change are stored in nonvolatile memory and will take effect the next time the emulator is powered off and back on again.

- 6 Turn OFF power to the emulator, and connect the emulator to your network. This connection can be made by using either the 15-Pin AUI connector or the BNC connector.

- 7 Set the rear panel dip switches to indicate the type of connection that is to be made:

Set switch 16 to one (1), indicating that a LAN connection is being made.

Set switch 15 to zero (0) if you are connecting up to the BNC connector, or set switch 15 to one (1) if a 15-pin AUI connection is made.

Set switch 14 to zero (0).

Set all other switches to zero (0).

#### Chapter 2: Connecting to a Host Computer To configure LAN parameters using the terminal interface

- 8 Turn ON power to the emulator card cage.

- **9** Verify your emulator is now active and on the network by issuing a **telnet** to the Internet Address. For example:

\$ telnet 192.6.94.2 <RETURN>

This connection will give you access to the built-in terminal interface. To exit from this telnet session, type <CTRL>d at the emulator prompt.

The next time LAN parameters need to be configured, telnet to the emulator and use the terminal interface lan command.

| If "telnet" does not access the emulator                                                                                                                                                                                                                                                            |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| You must use the telnet command on the host computer to access the emulator's built-in terminal interface. After powering up the emulator, wait a minute. It takes a minute before the emulator can be recognized on the network. Then try the telnet <internet address=""> command.</internet>     |  |

| If telnet does not make the connection:                                                                                                                                                                                                                                                             |  |

| Make sure you have connected the emulator to the proper power source and that the power light is lit.                                                                                                                                                                                               |  |

| Make sure the LAN cable is connected. Refer to your LAN documentation for testing connectivity.                                                                                                                                                                                                     |  |

| Make sure the rear panel communication configuration switches are set<br>correctly. Switch settings are only used to set communication parameters<br>when power is cycled (turned OFF and then ON again).                                                                                           |  |

| Make sure the Internet Address is set up correctly. You must use the RS-232/RS-422 port to verify that the Internet Address is set up correctly. While accessing the emulator via the RS-232/RS-422 port, run performance verification on the LAN interface hardware with the <b>lanpv</b> command. |  |

| If telnet makes the connection, but you see no terminal interface prompt (such as R>, M>, or U>):                                                                                                                                                                                                   |  |

| It's possible the emulator interface software is in the process of running a command (for example, if a repetitive command was initiated from telnet in another window). You can use <ctrl>c to interrupt the repetitive command and get the terminal interface prompt.</ctrl>                      |  |

| It's also possible for there to be a problem with the emulator firmware while<br>the LAN interface is still up and running. In this case, you must cycle power<br>on the emulator card cage.                                                                                                        |  |

3

## Connecting to the Demo Board

How to connect the emulator to the demonstration target system.

#### Installation

This chapter shows you how to connect the emulator to the demo target system which is shipped with the emulator. It also shows you how to verify installation by starting the emulator/analyzer interface for the first time.

## Step 1. Connect the emulator probe to the demo target system

1 With HP 64700 power OFF, connect the emulator probe to the demo target system. Notice the white line labeled 144-TQFP on the probe (white line with no label on MC68LC302 and MC68EN302). It will be above, and parallel with the white line on the demo target system when the emulator probe is connected properly.

When you install the probe into the demo board, be careful not to bend any of the pins. Do not insert the probe of the MC6830x emulator into the demo board socket incorrectly. Be very careful.

## Chapter 3: Connecting to the Demo Board Installation

2 Connect the power supply cable from the emulator to the demo target system. The 3-wire cable has one power wire and two ground wires. When attaching the 3-wire cable to the demo target system, make sure the connector *is aligned properly* so that all three pins are connected.

#### Step 2. Apply power to the HP 64700

|          | Step 3. Verify the performance of the emulator                                                                          |  |

|----------|-------------------------------------------------------------------------------------------------------------------------|--|

| 1        | Establish communication with the emulator from your host or ASCII terminal and obtain a prompt (such as $\mathbf{R}$ ). |  |

| 2        | Enter: <b>pv 1</b> <return></return>                                                                                    |  |

|          | The emulator will print the results of its test, followed by a prompt.                                                  |  |

| 3        | Enter: <b>ver</b> <return></return>                                                                                     |  |

|          | The emulator will print some version numbers and the status of the memory modules on the probe, followed by a prompt.   |  |

| 4        | 4 Enter: <b><ctrl>d</ctrl></b>                                                                                          |  |

|          | This command will end the emulation session.                                                                            |  |

| 5        | If the emulator reported any failures, refer to Chapter 6, "Solving Problems."                                          |  |

| Examples | If you are using a LAN, you can use the telnet capability with the built-in Terminal Interface:                         |  |

|          | 1 From your host computer, enter the command:<br>telnet <emulator_name>.</emulator_name>                                |  |

|          | 2 Now enter the command: <b>pv 1</b>                                                                                    |  |

|          | Note: the HP 64700 telnet capability is not supported by Hewlett-Packard.                                               |  |

4

# Connecting the Emulator to a Target System

Things you need to know to successfully connect the emulator to a target system and overcome problems you may encounter.

### Plugging The Emulator Into A Target System

The following paragraphs help you understand the emulator. Equivalent circuits are shown, followed by a list of devices that you may need to use to overcome mechanical and electrical constraints in your target system.

#### Understanding an emulator

An emulator is a tool intended for debugging software, and the interactions between software and hardware. Although emulators can help in debugging certain hardware problems, catastrophic problems often require use of other tools, such as a timing analyzer with a preprocessor, or an oscilloscope. To use an emulator effectively, you need to understand its capabilities and limitations, and how it interacts with your target system. This chapter discusses limitations and interactions of an emulator, as they relate to your target system.

An emulator is designed to be electrically and functionally equivalent to the processor it emulates. Some microprocessor signals are electrically isolated from their counterparts on the target system connection. This is done for both electrical and functional reasons. The impact of these circuits is calculated and presented in the emulator specifications beginning on page 145 for the MC68302 and MC68EN302 and on page 189 for the MC68LC302.

#### Target system design

A target system that is designed around the worst-case specifications of an MC6830x-series processor should work with the emulator. Ideally, you would use the emulator specifications listed in this manual when designing your target system, instead of the processor specifications. But usually a target system has already been designed and prototyped before the emulator is introduced. If certain circuits in your target system do not allow for variations in the microprocessor specifications, compare the relevant emulator specifications to evaluate their impact on your target system. By keeping the differences between emulator specifications and processor specifications in mind while you design your target

system, you can save hours of debugging time when you plug the emulator into your target system.

#### **Buffering and AC specifications**

Most signals going to and from the emulator are not intercepted. Of those that are, for example the data bus, nearly all are gated using analog transmission gates, which introduce very little delay in these signals. Because these gates don't buffer the signal when they are on, the target system and the internal signals of the emulator are effectively connected. This typically results in the target system seeing more capacitance because of emulator circuitry and traces than with the processor alone. The net result is that even though these transmission gates don't add a lump sum delay, the capacitance may slow the edges of the signal, resulting in an extra delay.

The CLKO signal is always buffered to the target with a CDC392 clock driver. This improves drive capability to the target system and signal quality to the emulator. The ability to change clock drive strength is not supported by the emulator.

Various strobes and control signals (AS, UDS, LDS, R/W, IACK7, CS0-CS3, and FC0-FC2 in the MC68302 and MC68EN302, and AS, OE, WEH, WEL, and CS0-CS3 in the MC68LC302) are normally gated using transmission gates but can optionally be buffered through 16V8 or 20V8 PALs. Buffering may improve signal quality with certain target systems but at the expense of additional delay and slightly lower V<sub>OH</sub>. It is recommended that strobes and control signals NOT be buffered unless the particular target system clearly benefits from buffering.

The strobes AS, UDS, LDS, and IACK7 (when not used as PB0) in MC68302 and MC68EN302, and AS, OE, WEH, and WEL in MC68LC302 are grouped together for buffering or un-buffering. R/W, the chip selects, and the function-code lines each can be buffered or unbuffered independent of the strobes. This buffering can be controlled through the configuration dialogs in the graphical interfaces (see the on-line help for details). In the built-in terminal interface, the **cf bufstrbs**, **cf bufrw**, **cf bufcs**, and **cf buffc** commands (and **cf bufwe** in the MC68LC302) control buffering. Different timing specifications are given depending on the selections chosen for these configurations.

Examine the AC specifications of the emulator to evaluate their differences from the microprocessor specifications. Because the emulator does not behave exactly like the microprocessor, you may need to examine signal quality and take appropriate steps to compensate for differences.

Chapter 4: Connecting the Emulator to a Target System **Plugging The Emulator Into A Target System**

#### **DC** specifications

Examine the DC specifications of the emulator to evaluate their differences from the microprocessor specifications. The emulator adds input leakage current ( $I_{IN}$ ) which is included in the  $I_{IL}$  and  $I_{IH}$  specifications, and additional capacitance which is included in the  $C_{IN}$  specifications. The  $C_{EL}$  specifications include how much additional capacitance the emulator places on outputs from the microprocessor which go to the target. This can be used in calculating output drive derating factors for all signals except CLKO, which is buffered before it is sent to the target.

When AS, UDS, <u>LDS</u>, <u>R/W</u>, <u>IACK7</u>, <u>CS0-CS3</u>, <u>or FC0-FC2</u> on the MC68302 and MC68EN302, or AS, OE, WEH, WEL, and CS0-CS3 on the MC68LC302 are configured to be buffered, output drive capability will meet or exceed that of the microprocessor itself except for V<sub>OH</sub> which is slightly lower.

#### **Target power**

The emulator uses power from the target system to operate the emulation processor and some pullup resistors. Target power is sensed to make sure the emulator does not drive the target system until the target is powered up.

#### Caution

**Possible target system damage.** Because of the protections designed into the emulator, always turn power on in the emulator before turning power on in the target system. Always turn power off in the target system before turning off power in the emulator.

#### **Clock information**

MC6830x processors can operate in either of the following two clock modes:

- Clocked from an oscillator with CMOS levels supplied to EXTAL.

- Clocked from a crystal connected to EXTAL and XTAL.

The emulator supports both of the above clock modes. For flexibility when supporting these clock modes, the emulator allows operation from either an external or internal clock source, as follows:

- External clocks are clocks supplied from an oscillator within the target system.

- Internal clocks are clocks supplied from either an oscillator or crystal plugged into the 14-pin clock socket on top of the emulation probe.

Crystal operation is only supported when using internal clocks because cable capacitance may make external crystal operation unreliable. If you wish to use crystal operation, the clock module kit (included with the emulator) provides three standard frequency crystal modules. If you wish to use a crystal frequency that is not provided in the clock module kit, you can build your own circuit on either User 1 (Module A) or User 2 (Module B) of the clock module kit. These two modules differ only in the land pattern for the surface mount crystal. Choose the module that best fits your crystal.

## Chapter 4: Connecting the Emulator to a Target System **Plugging The Emulator Into A Target System**

| Microprocessor and                    | Clock source for emulator                                                                           |                                                                                                                                           |  |

|---------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| Clock Mode                            | Internal<br>cf clk = int                                                                            | External<br>cf clk = ext                                                                                                                  |  |

| MC68302 and MC68EN302 with oscillator | oscillator module:<br>20 MHz supplied by HP or<br>8-25 MHz supplied by user                         | Any oscillator or crystal module.<br>This provides a working internal<br>clock which must be detected<br>during interface initialization. |  |

| MC68302 and MC68EN302 with crystal    | 24 MHz (Module E), or<br>User 1 (Module A), or<br>User 2 (Module B)                                 | Not supported.                                                                                                                            |  |

| MC68LC302 with oscillator             | oscillator module:<br>20 MHz supplied by HP or<br>0-25 MHz supplied by user                         | Any oscillator or crystal module.<br>This provides a working internal<br>clock which must be detected<br>during interface initialization. |  |

| MC68LC302 with crystal                | 32.768 kHz (Module C), or<br>4.194 MHz (Module D), or<br>User 1 (Module A), or<br>User 2 (Module B) | Not supported.                                                                                                                            |  |

The following table shows you how to configure the emulator for the supported clock modes.

#### Note

To run performance verification on the emulator, the demo/test board must be attached to the emulator probe instead of the flexible adapter cable, the +5V power cable from the emulator frame to the demo/test board attached, and the emulator internal clock source must contain an oscillator or crystal circuit with an appropriate frequency. If the internal clock source is missing, performance verification will fail.

#### Chapter 4: Connecting the Emulator to a Target System Plugging The Emulator Into A Target System

The clock socket on top of the emulation probe is a 14-pin DIP socket, accessible without removing the probe top cover. You can install a standard 14-pin DIP CMOS oscillator of any frequency that is approporiate for the version of MC6830x processor being emulated. The white dot beside the clock socket indicates pin 1. Pin 1 provides Oscillator Enable (active high) for oscillators that need it. A 20-MHz CMOS oscillator is included with the emulator for use as the internal clock source.

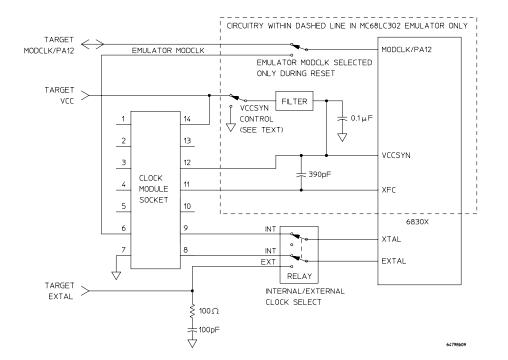

The diagram below shows the pinout of the clock socket on the MC68302 and MC68EN302 emulator probes. When using the 68LC302 emulator, pins 4, 6, 11, and 12 also have connections. Refer to the schematic on page 60 to see their usage.

If you are using an external clock source, you still must have an oscillator or crystal clock module installed. It must be detected during initialization of the graphical user interface. To run PV, you must install an appropriate oscillator or crystal in the clock socket. Performance verfication can only be run in the internal clock mode. A relay is used to switch between external and internal clock sources so no additional delay is added from the target EXTAL signal to the microprocessor. The XTAL signal from the microprocessor is not sent to the target system because external crystal operation is not supported.

The CLKO signal out of the microprocessor is the most important signal to the emulator because all system timing is derived from it. The CLKO signal from the microprocessor is always buffered to the target to isolate any target reflections on the target CLKO signal from the emulator. For proper operation, the CLKO signal must always be available to the emulator. It is possible to turn off CLKO from the microprocessor by setting both bits 14 and 15 of the CLKOCR register (address \$0FA) to 1. If CLKO is turned off, the emulator will indicate a *Slow Clock* prompt; a reset must be done to recover from this condition. It is also possible to change

the drive strength to 2/3 or 1/3 by setting these two bits to values other than zero. In this case, the emulator may appear to work but performance will be impaired. Make certain your target program never sets bits 14 and 15 of the CLKOCR register (address \$0FA) to anything but zero.

#### Selecting a clock module

If you can, use the clock circuitry from your target system to clock the emulator. If you must use an internal clock, ensure you have installed the correct clock module in the emulator probe before turning on the emulator.

The emulator is shipped with a 20-MHz CMOS oscillator for use as an internal clock source. You may use your own CMOS oscillator or build up a DIP header containing your own crystal circuit (see the *Motorola MC68302 User's Guide* for details). When using the demo/test board that is supplied with the emulator, if you choose external clock source, the demo/test board will supply a 25-MHz CMOS level clock.

If you wish to install a new clock module, the following guidelines will help you select the one that is correct for your application.

- If the target system uses a CMOS oscillator and you will clock your emulator from that oscillator:

- Configure emulator for external clock (cf clk=ext).

- Any clock module can be plugged in on the emulator probe. A valid internal clock is required during initialization of a graphical user interface.

- If the target system uses a 32.768-kHz crystal (MC68LC302 only):

- Configure emulator for internal clock (cf clk=int).

- Plug in Module C from the clock module kit (32.768 kHz crystal).

- MODCLK = 1, driven by emulator.

- If the target system uses a 4.194-MHz crystal (MC68LC302 only):

- Configure emulator for internal clock (cf clk=int).

- Plug in Module D from the clock module kit (4.194 MHz crystal).

- MODCLK = 0, driven by emulator.

- If the target system uses a 24-MHz crystal (MC68302 or MC68EN302):

- Configure emulator for internal clock (cf clk=int).

- Plug in Module E, 24-MHz crystal module.

- If you need to design your own clock module:

- Use Module A (User 1) or Module B (User 2). The modules are the same except for the land pattern for the crystal. Be careful to ensure that your crystal connects properly to the land pattern of the module.

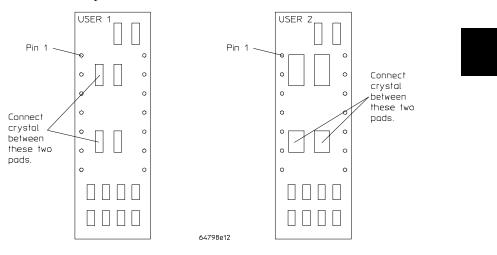

- Design your clock module using the module schematics on the next page, and the USER1/USER2 diagrams below to help you place your components.

Notes when designing a clock module for the MC68LC302 emulator:

- To make the emulator pull MODCLK low during reset, load a 0 to 215-ohm resistor in R5 (R15 for User 2).

- To make the emulator pull MODCLK high during reset, load a 0 to 215-ohm resistor in R4 (R14 for User 2).

- To make the emulator drive VCCSYN high (to enable the PLL), load a 0 to 215-ohm resistor in R6 (R16 for User 2). If R6 (R16) is not loaded, VCCSYN will be connected to GND and the PLL will not be enabled.

### **Clock module circuits**

#### Emulation Probe circuitry associated with the installed clock module:

#### Individual clock modules:

#### Clock module circuit details

Resistor R6 in the clock module completes a circuit that allows the emulator to obtain target VCC through the VCCSYN control switch. This switch supplies VCCSYN to the microprocessor where it enables the PLL in the microprocessor. Load a 0 to 100-ohm resistor for R6. Without resistor R6, the VCCSYN input of the microprocessor will be connected to ground and the PLL will be disabled.

The filter is an inductor-capacitor network that provides fine filtering of Target VCC to the microprocessor.

During reset, the emulator drives MODCLK to the microprocessor, and the value on the MODCLK/PA12 pin from the target system is ignored. During this time, the value supplied from clock module pin 6 either pulls MODCLK high or low, depending on whether you installed R4 or R5 in the clock module. During all non-reset times, the target system controls the signal on the MODCLK/PA12 pin.

The schematics show that target VCC is unused. It provides operating power to oscillators when they are plugged into the clock socket.

For an external oscillator clock source, the emulator terminates the EXTAL signal with 100 ohms in series with 100 picofarads.

#### Testing your custom crystal clock circuit

To determine if your custom crystal clock circuit operates properly, first make sure the emulator power is turned off and the emulator is plugged into the demo/test board. Then install your custom crystal header into the clock socket on the emulator and power up the emulator. In the built-in terminal interface, the **cf clk** command selects either an internal or an external clock source. The default from power-up is internal. The emulator contains logic which can determine the frequency of internal or external clock sources by measuring the CLKO signal out of the microprocessor. Use the **info clock** terminal interface command to display the clock frequency and source. The frequency should be near what you expect for the crystal you are using. If the frequency is 0.000 MHz or the wrong value, the crystal circuit is not working properly. If the frequency is correct, run performance verification to ensure the emulator will function with this internal clock source.

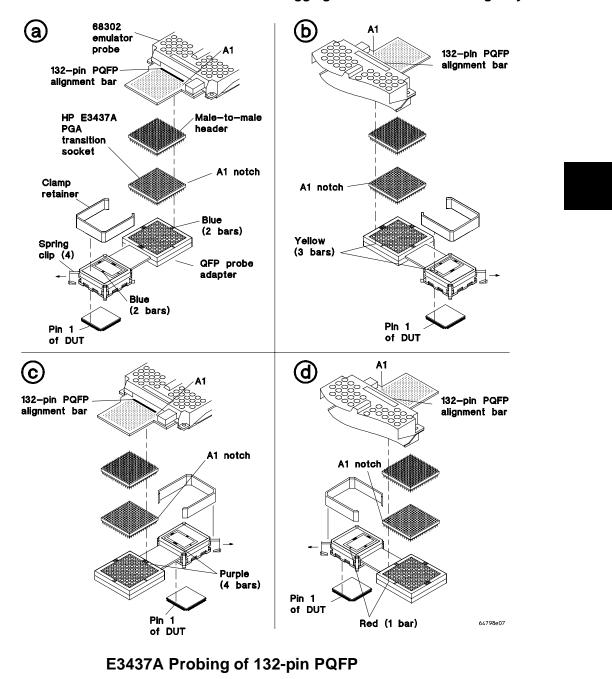

# Connecting the emulator to an MC68302 target system

This emulator supports connections to 132-pin PQFP and 144-pin TQFP package types for the MC68302. It also supports connections to the PGA pinout of older MC68302 microprocessors. Before connecting the emulator, a 132-pin PQFP or 144-pin TQFP "dummy part" (a mechanical sample with no internal connections) must be soldered onto the target system in place of the microprocessor. This is necessary because an MC68302 microprocessor has no facility to tri-state all of its signals. It is best to solder the dummy part onto the target system using automated surface mounting equipment to give more reliable probing. Hand soldering may result in solder wicking up the leads, which can prevent the probe adapter cable assembly from making good contact.

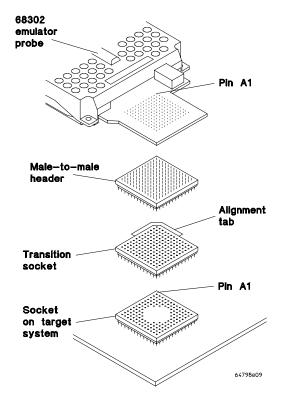

If connecting the emulator to a target system PGA connector, remove the microprocessor from the target system and install the transition socket (listed in Chapter 7).

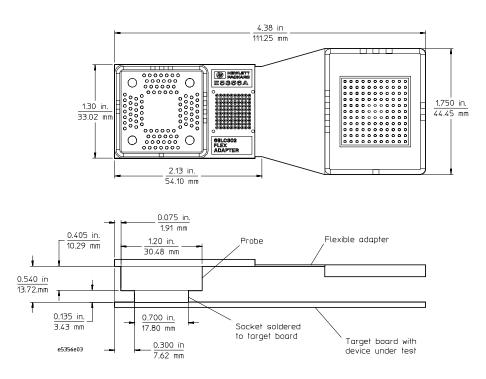

The emulator probe pod is normally connected to the target system using one of the available probe assemblies with their flexible adapter cables (see the following pages for connection details). The specifications given in this manual (page 145, and page 189) include use of the appropriate adapter cable. The probe assembly kits, which include dummy part kits, are listed in Chapter 7, Parts List (page 131).

The keep-out area is shown in your probing hardware manual. This shows the space required on your target system to allow connection of the probing hardware.

See Also: The documentation included in the probe kits for detailed instructions.

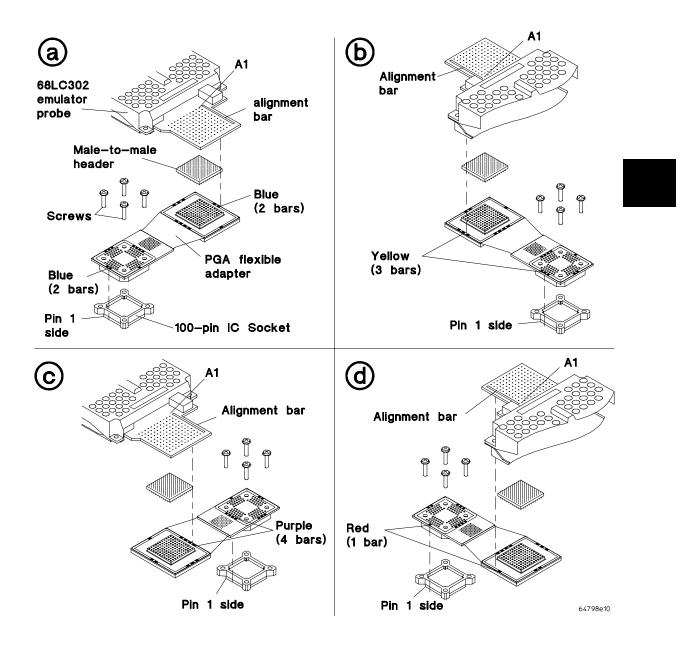

The 144-pin and 132-pin adapter cables can be installed in one of four orientations (each at right angles to the others). This allows flexibility in attaching the probe when target system components interfere. Select the orientation (shown on the next pages) that best suits your target system, and note the position of Pin 1 on the microprocessor (dummy part) on your target board.

There are two labels with color coding and bar coding on the adapter cables; use them to ensure correct orientation when the probe adapter is connected to the emulator. Note the color or count the bars on the edge of the probe that is placed over the Pin 1 side of the target microprocessor chip. (For example, Pin 1 of the microprocessor chip may be along the side that is color coded yellow, or along the side that has three bars.) There is a corresponding edge on the PGA end of the

adapter cable; it has the same color code and bar code. For example, the PGA connector of the MC68302 emulator probe has a white bar and corresponding notation "144-TQFP" and a second white bar and corresponding notation "132-PQFP". These bars indicate the side where Pin 1 occurs on the emulator probe 13x13 PGA connector for a 144-pin TQFP target and for a 132-pin PQFP target. If you are making connections to an MC68302 dummy part, connect the "144-TQFP" side of the emulator probe 13x13 PGA end of the 132-PQFP" side of the emulator probe 13x13 PGA connector into the PGA end of the 144-pin TQFP adapter cable, or connect the "132-PQFP" side of the emulator probe 13x13 PGA into the PGA end of the 132-pin PQFP adapter cable. Note that the 132-pin PQFP adapter cable must include a "transition board" which converts the 12x12 PGA at the end of the PQFP adapter cable to the 13x13 PGA used by the emulator probe. This "transition board" is included in the E3437A kit.

If you use the PGA transition socket to connect directly into the PGA connector on your target system, the position of pin 1 on your target system pinout governs PGA connector orientation.

Caution

Equipment damage. The connections between the emulator probe, flexible probe adapter cable, and microprocessor (dummy part) on the target board are delicate and must be done with care. Refer to the Operating Note supplied with the flexible adapter cable for specific instructions when making the connection.

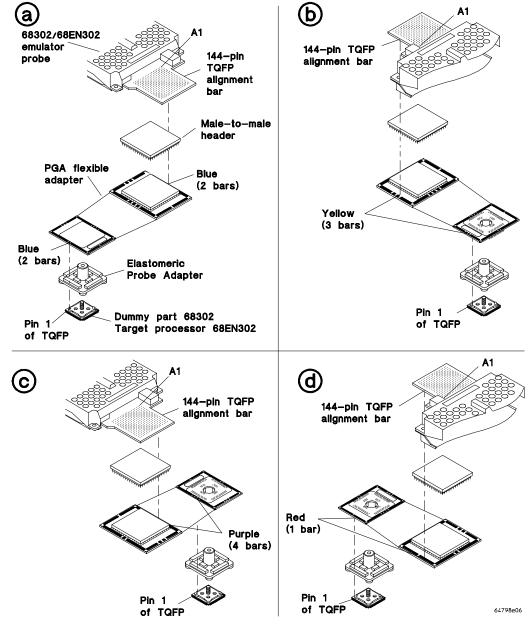

# Connecting the emulator to an MC68EN302 target system

This emulator supports connections to a 144-pin TQFP package type. An MC68EN302 emulator connects directly to the target microprocessor, not to a dummy part. The MC68EN302 can tri-state its signals.

Connect the emulator probe pod to the target system using the 144-pin probe assembly shown on the following pages. The specifications given in this manual (page 145) include use of the adapter cable. The probe adapter and flexible adapter cable are listed in Chapter 7, Parts List.

Observe the instructions and precautions for installing the 144-pin connector hardware described in the paragraph titled, "Connecting the emulator to an MC68302 target system," above.

65

E5336A/E5338A Probing of 144-pin TQFP

E5367A Probing of target system PGA

# Connecting the emulator to an MC68LC302 target system